If the clock input to a T flip-flop is 200 MHz and the input is tied to 1, what is the output, Q of the T flip flop? - Quora

Design of an All-Digital Synchronized Frequency Multiplier Based on a Dual-Loop (D/FLL) Architecture

Design of an All-Digital Synchronized Frequency Multiplier Based on a Dual-Loop (D/FLL) Architecture

Design of an All-Digital Synchronized Frequency Multiplier Based on a Dual-Loop (D/FLL) Architecture

A clock frequency doubler using a passive integrator and emitter-coupled comparator circuit | Semantic Scholar

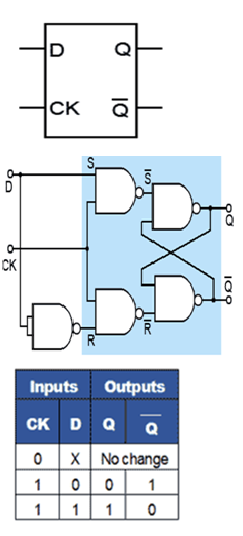

Figure 1 from Design of high frequency D flip flop circuit for phase detector application | Semantic Scholar